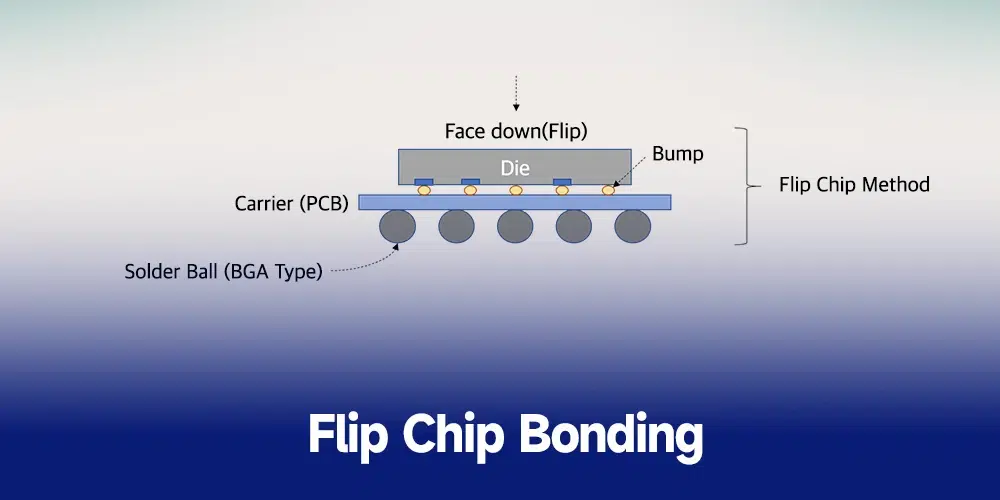

Flip chip packaging is a foundational interconnect approach used in advanced semiconductor systems where electrical performance, power integrity, and thermal efficiency are critical. By eliminating long wire bonds and replacing them with direct, face-down interconnections, flip chip packaging supports the density and bandwidth requirements of modern processors and memory devices.

Why Flip Chip Packaging Is Used in Advanced Systems

As semiconductor devices scale, traditional wire bonding becomes a limiting factor due to inductance, routing congestion, and restricted I/O placement. Flip chip packaging addresses these constraints by distributing connections across the die surface rather than along its edges.

Its architecture reduces electrical path length, supports higher current delivery, and enables efficient heat transfer from the active silicon into the package and cooling solution. These characteristics make flip chip packaging the dominant choice for high-performance CPUs, GPUs, accelerators, and memory subsystems.

Core Elements of a Flip Chip Package

Die Interface and Pad Engineering

The silicon die includes metal pads exposed through passivation layers. These pads are engineered with under-bump metallization stacks that promote solder attachment, limit diffusion, and manage current density. Redistribution layers may be added to reposition I/O into an optimized area array, allowing designers to balance pitch, routing complexity, and reliability.

Interconnect Formation

Electrical connections are formed using either solder bumps or copper pillar structures. Solder bumps offer cost efficiency and high throughput, while copper pillars provide improved current handling, controlled stand-off height, and finer pitch capability. Alternative conductive adhesive approaches exist for low-temperature assembly but require careful evaluation of long-term stability.

Substrate and Interposer Selection

The substrate serves as the mechanical and electrical interface between the die and the system board. Organic substrates are commonly used for their routing density and manufacturability, while ceramic substrates are selected for applications requiring higher thermal conductivity or RF stability.

For bandwidth-intensive designs, silicon interposers enable short, dense connections between logic and memory devices. Glass substrates are emerging as an alternative due to their low electrical loss and adjustable thermal expansion characteristics.

Stress Management Materials

Underfill materials are introduced to mechanically reinforce the solder joints and manage stress caused by thermal expansion mismatch between silicon and the substrate. Material selection focuses on adhesion, modulus, glass transition temperature, and fatigue resistance. The underfill strategy is a primary determinant of long-term reliability.

Environmental Protection

Encapsulation materials protect the assembly from moisture ingress, mechanical damage, and contamination. Mold compound properties influence package warpage, moisture sensitivity, and resistance to delamination during thermal processing.

Flip Chip Assembly Flow

Wafer-Level Interconnect Preparation

Interconnect structures are formed at the wafer level through metallization and electroplating processes. Copper pillars and solder caps are precisely defined to control pitch, height, and coplanarity, all of which impact downstream assembly yield.

Substrate Conditioning

Substrate pads are prepared with appropriate surface finishes to ensure solderability. Flux application or fluxless processing methods are selected based on pitch, oxidation sensitivity, and cleanliness requirements.

Die Placement and Bonding

High-precision equipment aligns and places the die onto the substrate. During solder reflow or thermo-compression bonding, interconnects form, and surface tension assists in achieving the final alignment. At very fine pitch, pressure-assisted bonding methods are required to ensure joint integrity.

Joint Formation and Reinforcement

Controlled thermal profiles establish metallurgical bonds between the die and substrate. Underfill materials are then introduced and cured to reinforce the assembly and improve resistance to thermal cycling and mechanical stress.

Inspection and Validation

Non-destructive inspection methods such as X-ray imaging and acoustic microscopy verify joint integrity and detect voids or delamination. Electrical testing confirms connectivity before final integration.

Design and Reliability Considerations

- Electrical and Thermal Performance: System requirements should be defined early. Flip chip interconnects shorten current paths, lowering inductance and voltage drop while enhancing heat transfer. Copper pillars support fine pitch and high current with controlled standoff and reduced parasitics.

- Material Compatibility: Substrates and interconnect materials must be compatible with the operating conditions. Organic ABF supports dense routing, while ceramic AlN offers higher thermal conductivity and low RF loss. CTE, Tg, dielectric properties, and moisture resistance should align with reliability targets.

- Manufacturing Readiness: Reliable assembly depends on process control at the target pitch. Placement accuracy, reflow atmosphere, and readiness for thermo-compression or non-conductive film processes are key. Inspection coverage and compliance with board-level reliability standards are required.

- Integration Scalability: Package choices should support future growth and expansion. Silicon interposers enable higher bandwidth integration, while glass substrates reduce loss and warpage at larger sizes.

Who Benefits from Flip Chip and Flip Chip Package Technology

- High-Performance Computing and Processing: Flip chip packaging is commonly used in CPUs, GPUs, accelerators, and high-bandwidth memory devices where electrical performance and power delivery are critical. The short interconnect paths reduce parasitic effects and support higher data rates, making the technology suitable for compute-intensive and data-heavy applications.

- Designs with High I/O Density Requirements: Products that require a large number of input/output connections often exceed the practical limits of wire bonding. Flip chip and flip chip package technology allow I/O to be distributed across the die surface, enabling higher pin counts, finer pitch, and more efficient routing.

- Thermally Constrained Systems: Applications with elevated power density benefit from flip chip’s direct heat transfer path from the die to the substrate and cooling solution. This makes the technology relevant for systems where junction temperature management has a direct impact on performance and reliability.

- Advanced and Scalable Integration Programs: Engineering teams developing multi-die architectures, silicon interposer-based designs, or 2.5D and 3D integration platforms often rely on flip chip packaging as a core interconnect. Its compatibility with advanced substrates and heterogeneous integration supports long-term scalability.

Flip chip packaging has become a core enabler for modern semiconductor systems that demand high electrical performance, robust power delivery, and efficient thermal management. By combining optimized interconnect structures, advanced substrates, and carefully engineered materials, flip chip and flip chip package technology provide a scalable foundation for today’s high-density, high-power designs. As architectures continue to evolve toward multi-die integration and higher bandwidth requirements, flip chip packaging will remain a critical platform for reliable, performance-driven semiconductor innovation.